# Pattern-Based Prefetching with Adaptive Cache Management Inside of Solid-State Drives

JUN LI, XIAOFEI XU, ZHIGANG CAI, and JIANWEI LIAO, Southwest University of China, China KENLI LI, Hunan University, China BALAZS GEROFI and YUTAKA ISHIKAWA, RIKEN Center for Computational Science, Japan

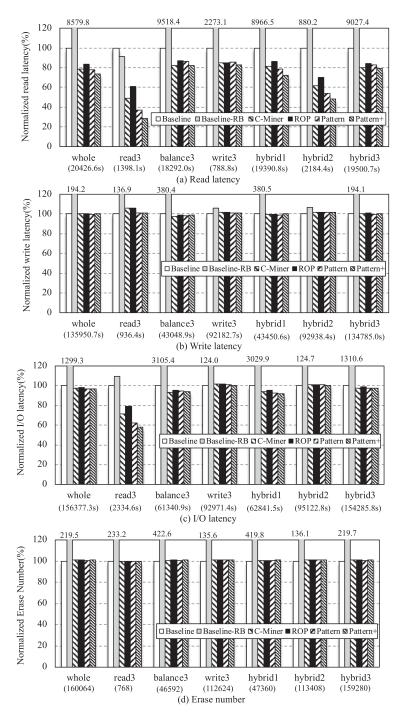

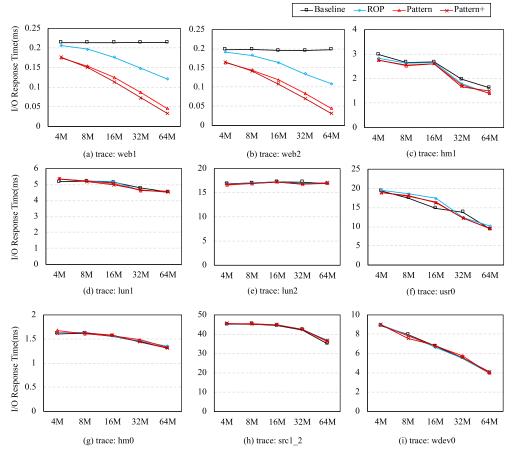

This article proposes a pattern-based prefetching scheme with the support of adaptive cache management, at the flash translation layer of **solid-state drives** (**SSDs**). It works inside of SSDs and has features of OS dependence and uses transparency. Specifically, it first mines frequent block access patterns that reflect the correlation among the occurred I/O requests. Then, it compares the requests in the current time window with the identified patterns to direct prefetching data into the cache of SSDs. More importantly, to maximize the cache use efficiency, we build a mathematical model to adaptively determine the cache partition on the basis of I/O workload characteristics, for separately buffering the prefetched data and the written data. Experimental results show that our proposal can yield improvements on average read latency by 1.8%–36.5% without noticeably increasing the write latency, in contrast to conventional SSD-inside prefetching schemes.

#### CCS Concepts: • Computer systems organization → Embedded software;

Additional Key Words and Phrases: SSDs, SSD cache, prefetching, frequent access pattern, adaptive cache management, I/O time

#### **ACM Reference format:**

Jun Li, Xiaofei Xu, Zhigang Cai, Jianwei Liao, Kenli Li, Balazs Gerofi, and Yutaka Ishikawa. 2022. Pattern-Based Prefetching with Adaptive Cache Management Inside of Solid-State Drives. *ACM Trans. Storage* 18, 1, Article 7 (January 2022), 25 pages.

https://doi.org/10.1145/3474393

© 2022 Association for Computing Machinery.

1553-3077/2022/1-ART7 \$15.00

https://doi.org/10.1145/3474393

This is a revised version. A preliminary version of this work was published in the Proceedings of 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE'20).

J. Liao works for Southwest University of China, and State Key Lab. for Novel Software Technology, Nanjing University, People's Republic of China.

This work was partially supported by National Natural Science Foundation of China (No. 61872299, No. 62032019), Chongqing Graduate Research and Innovation Project (No. CYB21110), Chongqing Talent (Youth, No. CQYC202005094), and the Opening Project of State Key Laboratory for and Novel Software Technology (No. KFKT2021B06).

Authors' addresses: J. Li, X. Xu, Z. Cai, and J. Liao (corresponding author), Southwest University of China, Chongqing 400715, China; emails: {junli95, nakamura}@email.swu.edu.cn, czg@swu.edu.cn, liaojianwei@il.is.s.u-tokyo.ac.jp; K. Li, Hunan University, Hunan 410082, China; email: lkl@hnu.edu.cn; B. Gerofi and Y. Ishikawa, RIKEN Center for Computational Science, Kobe 650-0047, Japan; emails: bgerofi@riken.jp, ishikawa@is.s.u-tokyo.ac.jp.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

#### **1 INTRODUCTION**

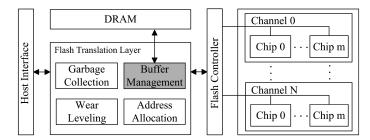

The NAND flash memory-based **solid-state drives** (**SSDs**) are commonly employed in PCs, data centers, and supercomputers, because of their virtues of small size, high data throughput, randomaccess performance, and low energy consumption [1–3]. Apart from a NAND flash array that holds data, an SSD device generally has a micro-controller and a **Random Access Memory** (**RAM**). To be specific, the micro-controller runs **Flash Translation Layer** (**FTL**) to deal with logical-physical address mapping, **garbage collection** (**GC**), and **wear-leveling** (**WL**) [4–7]. The RAM memory is used as the buffer inside of SSD<sup>1</sup> to cut down the number of write operations to the flash array, as well as keeping address mapping data structures [8, 9].

Data prefetching is a commonly used optimization scheme for disk-based file systems, where fetching data from the disk dominates the overhead of read operations [12]. Specifically, prefetching works well for target applications having regular access patterns on reads, such as database servers or some scientific computations [12, 17]. In an SSD setting, prefetching can mask read latency in flash data blocks, as the needed data were loaded into the RAM memory in advance. Consequently, it has started to be applied to a variety of SSD-based storage systems [13, 14, 20]. Note that the prefetching methods in the file system may run at the levels of virtual file system and file system, but the prefetching schemes inside of SSDs run at the level of SSD devices in the I/O stack.

Considering the memory size and processing power were limited in early SSDs, the main concerns of existing prefetching schemes were about the low computation cost and the low power consumption [20]. Then, most of them were involved with the operating system layer or even both the operating system layer and SSDs [13, 14], which must damage the natures of compatibility and transparency. Although some inside SSD prefetching schemes have been proposed, their prediction models were generally confined to the limited computation and memory resources [20].

We say that nowadays SSDs have large computing power in micro-controllers as well as more memory capacity inside. For example, the Cosmos OpenSSD platform [15], which is publicly released by the OpenSSD project, is equipped with more than 100 MB SDRAM and an embedded 1 GHz ARM CPU. Then, we argue that designing a (near) universal prefetching scheme inside of modern SSDs becomes available, and such inside prefetching approaches do have advantages of OS independence and use transparency. That is to say, such SSDs can be deployed in any context, as their micro-controllers are in charge of prefetching tasks.

In the case in which the prefetching functionality is enabled, the SSD cache is used to buffer not only the written data, but also the prefetched data. Conventional prefetching methods adopt a fixed portion of cache to buffer the prefetched data [13, 14, 20]. However, such fixed cache separation schemes cannot fit all I/O characteristics in varied applications. For example, the prefetched data are supposed to be enlarged while executing read-intensive applications in general. More specifically, some applications may change their read/write workloads during the lifetime, which indicates that data prefetching may work in some time windows of lifetime, but fail in other time windows. Then, in order to boost cache use efficiency, the division of write/prefetch cache<sup>2</sup> should depend on real-time factors in the workloads such as the read/write ratio and the prefetching accuracy.

To address the aforementioned issues, this article proposes an SSD-inside prefetching mechanism with adaptive cache management, to better improve I/O performance of SSDs. In summary, it makes the following contributions:

<sup>&</sup>lt;sup>1</sup> The terms SSD RAM memory and SSD cache are used interchangeably in this article.

<sup>&</sup>lt;sup>2</sup> The terms write cache and prefetch cache represent the cache space for buffering the written data and the prefetched data, respectively.

ACM Transactions on Storage, Vol. 18, No. 1, Article 7. Publication date: January 2022.

Fig. 1. The internal architectural overview in SSDs.

- (1) We propose a frequent access pattern-based prefetching scheme. It first mines the frequent access patterns from the history of read requests to stand for the address collections that are frequently read together. Then, it holds a matrix to maintain the pattern information and to carry out the pattern matching for directing data prefetching in the current time window.

- (2) We construct a mathematical model by considering several comprehensive factors, such as the read/write ratio and the historical prefetching accuracy, to support adaptive cache management. Then, it is able to more precisely adjust the partition of the prefetch cache and the write cache from case to case.

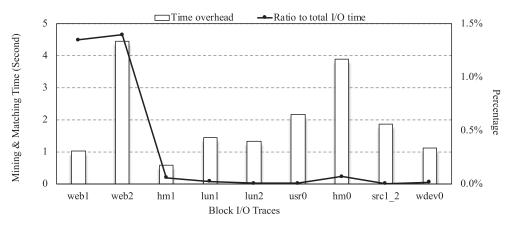

- (3) We offer preliminary evaluation on several disk traces of real-world applications. Apart from illustrating the performance benefits and scalability of our proposal, we specifically measure its time and space overhead and then assess their performance impacts.

Note that, as an extension of our previous work [35], only the last two contributions are new in this article. As our measurements indicate, the newly proposed data prefetching mechanism with adaptive cache management can further reduce the average read latency without noticeably increasing the write latency.

The rest of the article is organized as follows: the background knowledge and related work are introduced in Section 2. Section 3 specifically describes the proposed pattern-based prefetching scheme, and the adaptive cache partition management policy. Section 4 presents the evaluation methodology and reports the experimental results. Finally, the article is concluded in Section 5.

# 2 BACKGROUND AND MOTIVATION

## 2.1 SSD Architecture

Figure 1 shows an internal architectural overview of SSDs, including software and hardware components. Obviously, the main software layer of SSD is FTL, which takes charge of address mapping, garbage collection [9], wear-leveling [11], and buffer management. Specifically, the buffer management module running at FTL controls the use of **dynamic random access memory (DRAM)** of SSDs. In other words, not only the data structures of the address mapping table are saved in the buffer, but also the contents of write requests are temporarily cached in there to minimize the latency of responding write requests [8, 34].

# 2.2 Related Work

This section will briefly summarize the related work on data prefetching, SSD cache management, and other SSD-inside I/O optimization strategies.

Data prefetching and prediction models. In order to yield potential performance enhancements of storage systems, a variety of I/O history analysis-based I/O optimization mechanisms have been proposed and evaluated [16, 17]. In fact, data prefetching has to predict future possible read

requests to direct fetching data in advance. That is, the accuracy of request prediction is critical to the effectiveness and applicability of data prefetching. Then, hidden Markov models, neural networks, or other predictive algorithms are used to forecast I/O operations through analyzing I/O access patterns of the application [13, 18–20].

*Prefetching approaches focusing on SSD.* Flashy prefetching aims to enhance prefetching effectiveness for SSDs [13]. Though this method runs at the application level, it still relies on the **operating system** (**OS**) to collect the I/O traces and manage the cached data. *Lynx* is another prefetcher for SSDs but running at the OS layer in the Linux kernel [14]. It makes use of Markov chains to forecast future read requests, to guide reading the relevant data in advance.

Xu et al. [20] argued that OS-dependent prefetching lacks the advantages of use transparency and compatibility. They have thus proposed an SSD-inside prefetching mechanism at FTL, without any modifications to OS or applications. It adopts a divide-and-conquer algorithm to purposely reduce time and space complexity when conducting data prefetching, as they believe some SSDs may be resource-limited.

Considering modern SSDs are commonly equipped with a powerful compute processing unit and considerable size of RAM, we have proposed a prefetching approach to more accurately prefetch the expected data in our previous work [35]. In this method, we take advantage of the powerful SSD micro-controller to mine the frequent access patterns, which reflect the correlation among the occurred requests. Then, the process of prefetching data will be only triggered if a mined pattern is hit in the current time window.

SSD cache management for prefetched data. Cache approaches are mainly designed for RAM embedded in SSD (i.e., buffer cache). They generally intend to achieve cache hit rate improvement for maximizing the efficiency of cache usage. Considering both written data and prefetched data are buffered in SSD RAM, existing SSD prefetching schemes generally take advantage of a fixed cache division policy for buffering two kinds of data. For instance, in the resource-optimized prefetcher, the size of the prefetch cache is configured as 128 KB in evaluation experiments [20].

But, different applications have varied read/write footprints, so that it does not make sense to allocate an unchanging part of prefetch cache with respect to all cases. To address this issue, Xu et al. [35] have presented an empirical formula to divide the SSD cache into prefetch cache and write cache by separately holding the prefetched data and the written data, by referring to the read/write ratio in the applications.

SSD-inside optimizations. A considerable number of studies exploit the computational power of SSD controller by offloading the data-intensive tasks to the embedded cores of SSDs [21–23]. For example, Jun et al. [23] take advantage of in-storage processing capacity to perform big data analytics, by exemplarily integrating the *Morris-Pratt (MP)* string search engine in SSD. In addition, Pei et al. [24] propose *Registor*, which aims to eliminate I/O bottlenecks in unstructured data processing that needs *regex* search. To this end, they have designed a hardware engine for *regex* search and deployed it inside of flash SSD, to deal with data on-the-fly during data transmission from SSD to host.

#### 2.3 Motivations

We have analyzed certain block I/O traces of real-world applications, to disclose their probability distribution of read frequency on the address space and their number of hot read addresses at different execution stages.

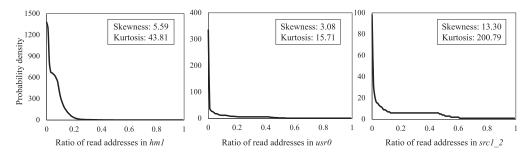

Figure 2 illustrates the results of probability distribution of three sampled applications in the Microsoft Research Cambridge block I/O trace collection [31]. They are  $hm_1$  (*read intensive*),  $usr_0$  (*read-write balanced*), and  $src1_2$  (*write intensive*). In the figure, the *X*-axis scales from 0 to 100%, which represents the proportion of read addresses ordering by their read counts, and the *Y*-axis

Fig. 2. The probability density of read frequency on the address space of some traces in the MSRC block trace collection [31] (spatial locality of block accesses).

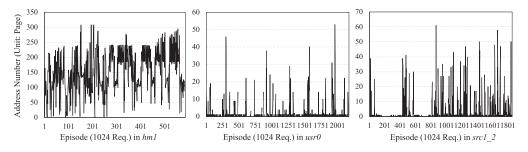

Fig. 3. The frequent read address space (i.e., not less than three) number in the whole application period (temporal locality of block accesses).

denotes the probability density of the read requests. Obviously, all block I/O traces show the locality of data access. That is to say, only a very small part of data (e.g., the left part of the *X*-axis in the figure) is intensively accessed after running the applications. Moreover, in order to characterize the location and variability of read frequency on block addresses in the traces, we calculate the measures of skewness and kurtosis [25] for better illustrating the access locality. As seen in the figure, these numerical values show that the read counts of block addresses are lack of symmetry and heavy-tailed. Then, we argue that only a small number of addresses have intensive read workloads.

OBSERVATION I. Applications read their data and obey the reference of space locality. Thus, prefetching the hot read data into the SSD buffer may contribute to better I/O performance caused by read hits.

Figure 3 shows the number of frequent read addresses in the lifetime of applications. The *X*-axis represents execution stages (each of them is composed of 1,024 requests), and the *Y*-axis shows the number of frequent accessed (i.e., not less than three) addresses. The results reveal that the hot read addresses differ from varieties of applications, and keep changing during different stages after replaying the selected block I/O traces. More importantly, this figure also reveals that certain read addresses will be intensively read in a short time period, which verifies the block accesses have temporal locality.

OBSERVATION II. The number of hot read addresses keeps changing at varied running stages in applications. Thus, dynamically adjusting the size of prefetch cache may boost the cache use efficiency.

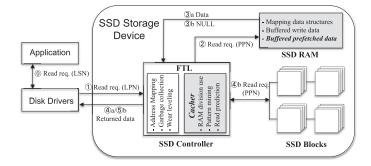

Fig. 4. High level overview of processing a read request in *Cacher-SSD*. It has two new features: (i) A software component of *Cacher* running at FTL, which is in charge of prefetching read data. (ii) The separate division of RAM dynamically adjusts to fit varied read/write workloads for holding the prefetched data.

Such observations motivate us to efficiently prefetch data into the SSD buffer by the following: (1) prefetching the frequently read data may increase prefetching hits and then boost read performance; (2) adjusting the size of the prefetch cache in an adaptive manner can contribute to better SSD buffer utilization.

## 3 PATTERN-BASED SSD PREFETCHING WITH ADAPTIVE CACHE MANAGEMENT

## 3.1 System Architecture

Figure 4 shows the high level overview of the proposed SSD-inside prefetching scheme, and we name such SSD as *Cacher-SSD*. In the case of a cache hit, the read request can be satisfied with the prefetched data buffered in SSD RAM. Otherwise, the data stored in the flash data blocks will be read and then forwarded to the application.

As seen, in addition to address mapping, garbage collection. and wear-leveling, a new software component of *Cacher* runs at FTL. Specifically, *Cacher* deals with mining patterns, representing patterns, and matching the identified patterns with the current requests, to direct data prefetching. Moreover, *Cacher* is in charge of cache space management, for separating the write cache and the prefetch cache. We do not modify the garbage collection policy and the wear-leveling policy in this work and assume *Cacher-SSD* continues to employ the default ones.

Figure 4 also illustrates the process of data prefetching in SSD devices. When a read request comes from an application, SSD controller receives the request and first searches the relevant data in the SSD RAM. If it hits in RAM buffer, then the cached data directly responds to the application. Otherwise, SSD controller tries to read the data from SSD blocks, and replies the data to the application. That is, if the prefetched data can be directly sent to the application, the read response time can be significantly cut down, but we must bear the prefetching overhead if the prefetched data are never hit.

## 3.2 Pattern-Based Prefetching

To precisely direct data prefetching, we propose pattern-based prefetching. Specifically, we refer to the correlation of data addresses as a request pattern, which is a special set of address items (that may be accessed together in a short period). Then, while some addresses in the pattern have been requested, the proposed scheme will fetch the data in the remainder addresses into the SSD cache in advance, as it believes other addresses in the pattern are most likely to be accessed soon.

| LSNs Patterns                             | 0   | 1 | 2 | 3 | 4 | k-1 | k | k+1 | ••• | n |

|-------------------------------------------|-----|---|---|---|---|-----|---|-----|-----|---|

| $\mathbf{P_0}\{0, 1, 3, k, k+1, n\}$      | 1   | 0 | 0 | 0 | 0 | 0   | 1 | 1   |     | 0 |

| <b>P</b> <sub>1</sub> {0, 2, 4, k-1, k+1} | 1   | 0 | 0 | 0 | 0 | 0   | 0 | 1   |     | 0 |

|                                           | ••• |   |   |   |   |     |   |     |     |   |

| $\mathbf{P_m} \{1, 3, 5, 7, k-1\}$        | 0   | 1 | 0 | 0 | 0 | 0   | 0 | 0   |     | 0 |

Fig. 5. Matching matrix of requests and patterns. Note that we use 1 representing the corresponding logical sector number is in a specific pattern, and it has been accessed since the last processing round, and utilize 0 standing for other cases.

3.2.1 Identifying and Modeling Frequent Access Patterns. The process of exploring access patterns can be addressed by the following two steps:

Step 1: The problem of mining the frequent patterns in our scenario can be described as follows: Let  $T = \{a_1, a_2, ..., a_n\}$  be a set of logical addresses of *n* requests in the I/O track. The aim is to discover a collection of frequent patterns from the input I/O trace of *T*. A frequent access pattern can be expressed as  $P_i = \{a_k, ..., a_x\}$ , where all logical addresses of requests, such as  $a_k$  and  $a_x$ , appear multiple times in *T*.

We take advantage of a widely used frequent item set mining approach called as the *FP-Growth* algorithm [26], to unearth frequent patterns by analyzing the requests in the previous time window. To be specific, the *FP-Growth* algorithm takes advantage of a divide-and-conquer strategy to extract frequent item sets without using candidate generations, so that it is efficient and scalable for mining both long and short frequent patterns. The core of this approach is the usage of a special data structure named **frequent-pattern tree** (*FP-tree*), which retains the itemset association information [26]. Consequently, by utilizing *FP-Growth*, we can acquire a number of frequent item sets, such as { $Add_1$ ,  $Add_2$ ,  $Add_3$ , 4}. This example pattern has three frequently requested addresses, and the number of 4 is the minimum support, which implies all three addresses have been accessed at least four times in all considered requests.

*Step 2:* After *Step 1*, it is possible to obtain many independent sets of access patterns. For the purpose of refining access patterns, we first sort them in descending order, by referring accessed time of addresses in patterns. Then, we check the access pattern that follows each occurrence of an identified pattern, and attempt to extend it. If more than half of elements in a specific pattern are also in another pattern, we carry out a union operation of two patterns, to form a new access pattern. Note that no extension to the access patterns should be performed if the number of access events in the extended pattern would exceed the upper limit.

3.2.2 Pattern Matching for Data Prefetching. The effectiveness of prefetching is primarily dependent on the prediction accuracy of future access requests [27]. The basic idea of pattern-based prefetching is to compare the current read requests with identified frequent patterns. In the case in which a (major) part of addresses in a specific pattern have been accessed, it forecasts other remaining addresses in the same pattern are most likely to be requested in the near future. As a result, the relevant data of remaining addresses are supposed to be read in advance.

Furthermore, the speed of predictions on future requests is also critical to the effectiveness of the prefetching mechanism. For the purpose of accelerating the matching process, we have introduced a matrix to reflect the relationship between the **logical sector numbers** (*LSNs*) of requests and the identified patterns. As illustrated in Figure 5, there are m identified patterns, and each row of patterns shows its member elements (labeled as request *LSNs*). Note that the set of columns is the

*LSN* union of the mined patterns in a given time window. In the case of dealing with a read request, all elements in the corresponding column will be set as 1, if its logical sector number is a part of the pattern.

Supposing the prefetching trigger condition is about more than a half of *LSNs* have been accessed in the pattern (i.e., the metric of *matching hit threshold* in Table 1 of Section 4.1), and the data of remaining addresses are supposed to be fetched in advance. We take a case shown in Figure 5 as an example. The pattern of  $P_0$  has six *LSNs* of (0, 1, 3, k, k+1, n), in which 0, k, and k+1 were requested. If the coming request targets at address of n, the process of data prefetching on *LSNs* of 1 and 3 will be activated, as a (major) part of addresses in this pattern have been accessed.

## 3.3 Adaptive Cache Management

The basic idea of adaptive cache management is to dynamically adjust the cache use on the basis of several impact factors. They are the numbers of read and write requests, the size of read and write space, and the numbers of read and write hits in cache in the previous time window.

First, we determine whether the prefetching functionality should be enabled or not after analyzing the statistical data of occurred I/O requests, by referring to Equation (1). That is to say, the prefetching functionality is supposed to be dynamically disabled in specific time windows if  $\tau$  is not less than a predefined value; otherwise, it will be supported.

$$\tau = \frac{W_{num}}{R_{num}} \times \frac{Prefetch_{miss}}{Prefetch_{all}},\tag{1}$$

where  $R_{num}$  and  $W_{num}$  are the numbers of total read and write requests in the previous time window. The parameters of  $Prefetch_{miss}$  and  $Prefetch_{all}$  indicate the numbers of non-hit prefetches and the total prefetches. Note that both of  $Prefetch_{miss}$  and  $Prefetch_{all}$  will be assigned as 1 if they are less than 1.

For the purpose of improving the efficiency of cache use in SSD, this section presents an adaptive cache partition policy that dynamically divides the write cache and the prefetch cache at different time windows of I/O processing. In our previous work [35], we proposed an adaptive cache division policy by referring to I/O characteristics of workloads, but it does not take the I/O frequency and address distribution into consideration.

In this section, we further build a mathematical model to estimate the return on cache use introduced by data prefetching, called *Pattern+*. Equation (2) demonstrates the overall return of prefetching data, consisting of the saved read response time (i.e.,  $T_1$ ) and the prolonged write latency due to write cache misses (i.e.,  $T_2$ ).

$$T = T_1 - T_2.$$

(2)

On the one side,  $T_1$  is positively correlated with the total number of read requests that are hit in the cache. Then, it can be illustrated as Equation (3).

$$T_1 = \alpha \times \gamma \times h, \tag{3}$$

where  $\alpha$ ,  $\gamma$ , and *h* denote the saved time caused by a read request being hit in the cache, the number of occurred read requests, and the proportion of read hits in the cache, respectively.

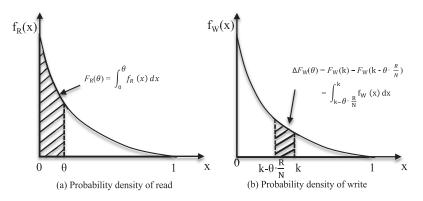

Specifically, the parameter of *h* depends on factors of the total size of prefetched data and what data have been prefetched. Section 2.3 discusses the probability distribution of read frequency on the address space of applications, which verifies only a small part of data are intensively accessed. Then, we build the model for adaptively adjusting the size of the prefetch cache, by referring to the probability distribution of block accesses. As seen in Figure 6(a), the *X*-axis scales from 0 to 100%, which represents the proportion of read addresses ordering by their read counts, and the

Fig. 6. The probability density of (a) read address frequency and (b) write address frequency.

*Y*-axis denotes the probability density of the read requests. That is to say,  $F_R(x) = \int_0^1 f_R(x) dx = 1$ . Figure 6(b) demonstrates the case of write requests, which is same as the read case.

Assume the  $\theta$  part of total read pages of data have been prefetched, shown in Figure 6(a), which are expected to be frequently accessed in the near future. The expression of  $F_R(\theta) = \int_0^{\theta} f_R(x) dx$  represents the ratio of reads on the  $\theta$  part of read data to the total number of reads. Considering the  $\theta$  part of read data are prefetched, the saved read response time (i.e.,  $T_1$ ) can be quantified by Equation (4).

$$T_1 = \alpha \times \gamma \times F_R(\theta). \tag{4}$$

On the other hand, the prefetched data must occupy the cache space, which was supposed to be used for buffering the written data, and is also shown in Figure 6. The initial ratio of the cached written data to all data is k, and  $\theta$  of read data are supposed to be prefetched, so that the reduction of probability of write hit can be expressed:

$$\Delta F_W(\theta) = F_W(k) - F_W\left(k - \theta \cdot \frac{R}{N}\right) = \int_{k-\theta \cdot \frac{R}{N}}^k f_W(x)dx$$

$$= \theta \cdot \frac{R}{N} \times \bar{f}_W\left(\theta \cdot \frac{R}{N}\right)$$

$$\approx \theta \cdot \frac{R}{N} \times f_W(k),$$

(5)

where  $F_W(k)$  means the ratio of the writes on the most frequently accessed k cached pages of written data to the total number of write operations. R and N represent the read address space and the total address space, respectively. The parameter of  $\bar{f}_W(\theta \cdot \frac{R}{N})$  is the average of write frequency to the pages within the range of  $(k - \theta \cdot \frac{R}{N}, k)$ , and  $f_W(k)$  is the write frequency to the page having the minimum access count in the range of  $(k - \theta \cdot \frac{R}{N}, k)$ .

In fact,  $f_W(k)$  indicates the minimum hit ratio of the cached written data; it will decrease when the hit ratio of cached written data degrades. As a consequence, the negative effect of prefetching can be defined as Equation (6).

$$T_2 = \beta \times \omega \times \theta \cdot \frac{R}{N} \times \bar{f}_W \left( \theta \cdot \frac{R}{N} \right), \tag{6}$$

where  $\beta$  is the saved time by buffering a page of written data, and  $\omega$  is the number of occurred write requests.

By referring back to Equation (5), the overall benefit of prefetching the most frequently accessed  $\theta$  part of read data can be measured by using Equation (7).

$$T_{\theta} = \alpha \times \gamma \times F_{R}(\theta) - \beta \times \omega \times \theta \cdot \frac{R}{N} \times \bar{f}_{W}\left(\theta \cdot \frac{R}{N}\right)$$

$$\approx \alpha \times \gamma \times F_{R}(\theta) - \beta \times \omega \times \theta \cdot \frac{R}{N} \times f_{W}(k).$$

(7)

According to the first-order condition of  $\frac{dT}{d\theta} = 0$ , and  $f'(\theta) < 0$ , it can be concluded that  $T_{\theta}$  will reach the maximum value in the case in which the condition of  $f(\theta^*) = \frac{\beta}{\alpha} \cdot \frac{\omega}{\gamma} \cdot \frac{R}{N} \cdot f_W(k)$  holds. In fact,  $\alpha$  and  $\beta$  are two constants depending on platform configurations; R, N,  $\gamma$ , and  $\omega$  are four statistical values collected from the occurred requests. The value of  $f_W(k)$  is the smallest write count to the buffered written data in the last time window.

The value of  $f(\theta^*)$  can be leveraged to split SSD cache for keeping the prefetched data. To this end, the read pages are sorted in descending order by referring their access counts. Then, the read data whose read counts are not less than  $R \cdot f(\theta^*)$ , should be initially loaded into the cache.

Then, we may have varied sizes of cache for buffering the prefetched data at different time windows. To achieve the goal of adaptive tuning the cache use for separately buffering the written data and the prefetched data, we evict either the cached written data or the prefetched data to load the new data, according to the partition ratio of cache use (i.e.,  $\theta_{cur}$ ) in the current time window.

Algorithm 1 shows the specifications on the adaptive cache replacement scheme. As read, line 11 identifies which part of cached data should be evicted. Specifically, it compares the current read pages (i.e., *rd\_pages\_cur*) to the read pages in the previous time window (i.e., *rd\_pages\_prev*), to determine which kind of cached data should be replaced by the new data. Lines 13–19 present the details of dealing with a missed write request. Lines 21–28 show the process of carrying out pattern-based prefetching.

#### 4 EXPERIMENTS AND EVALUATION

#### 4.1 Experiment Setup

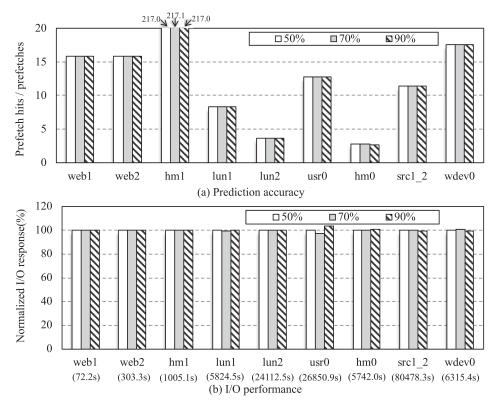

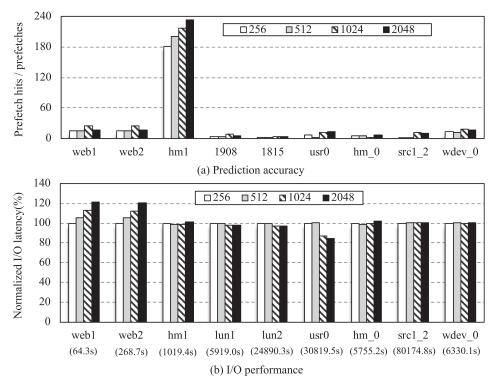

Considering SSD controller has limited computation power and memory capacity, we conducted tests on a local ARM-based machine that has an ARM Cortex A7 Dual-Core with 800 MHz, 128 MB of memory, and 32-bit Linux (ver 3.1). We have performed trace-driven simulation with *SSDsim* (*ver2.1*) on the local machine, which has a diverse set of configurations and supports of *TLC* flash simulation [33, 35]. We have integrated our proposal with *SSDsim*, for supporting data prefetching inside of SSDs. Table 1 presents the default settings of *SSDsim* in our experiments, which were decided by either referring to prior studies [33, 34], or carrying out sensitive tests. Specifically, *Cache size* is 32 MB by default, which is smaller than 0.1% of a 128 GB SSD device [36]. The relevant sensitive analysis on scalability with varying size of cache will be described in Section 4.5.2.

The metric of *Matching hit threshold* in the table implies the condition of triggering a prefetching operation after pattern matching, and the default value of *matching hit threshold* is configured as 50%, and the related sensitive analysis will be found in Section 4.5.1. The number of I/O requests in each time window is setting to 1,024, and the first 256 requests in the window are used to disclose frequent patterns to guide data prefetching. In addition, to reflect the impact of garbage collections, before running traces, the simulated SSD is aged to that with 70% of its capacity being used [33, 34].

We employed nine commonly used disk traces [28, 29]. Specifically, *websearch\_1* and *websearch\_2* (label as *web1* and *web2*) are collected from UMass Trace Repository [30], and the next five traces are from the block I/O trace collection of Microsoft Research Cambridge [31]. The remaining two recent block I/O traces are recently collected from a part of an enterprise **virtual**

| Parameters           | Values | Parameters             | Values   |

|----------------------|--------|------------------------|----------|

| Capacity             | 128 GB | Read time              | 0.075 ms |

| Page per block       | 64     | Write time             | 2 ms     |

| Page size            | 8K     | Cache read/write       | 0.001 ms |

| Cache size           | 32 MB  | Elements in pattern    | [2, 10]  |

| Fixed prefetch cache | 8%     | Matching hit threshold | 50%      |

Table 1. Experimental Settings of SSDsim (TLC Cell)

*Note:*  $\alpha$  and  $\beta$  in Equation (7) are then 0.074 ms and 1.999 ms.

| ALGORITHM 1: Adaptive cache replacement policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <b>Input</b> : args of <i>read_addr_space</i> , $\theta_{-cur}$ , $\theta_{-prev}$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| <b>Output</b> : completion of I/O processing in a time window;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| /* quantifying the number of pages for prefetched data */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| $_2 rd_pages_cur = read_addr_space \times \theta_cur;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| $_{3} rd_pages_prev = read_addr_space \times \theta_prev;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 4 /*0: replacing read pages, 1: replacing write pages*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 5 rep_flag = 0;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 6 /* processing requests in the current time window */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 7 for req in I/O Queue do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| s if $req \rightarrow addr$ hit in Cache then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 9 continue;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 10 end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| $rep_flag = rd_pages_cur \ge rd_pages_prev ? 1:0;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 12 /*evicting cached data and buffering new written data*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 13 if req is a Write then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

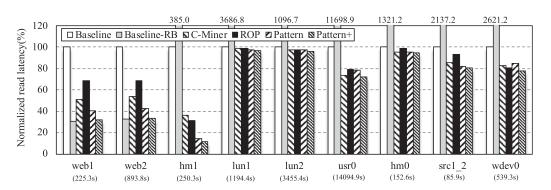

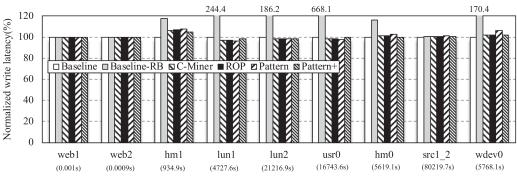

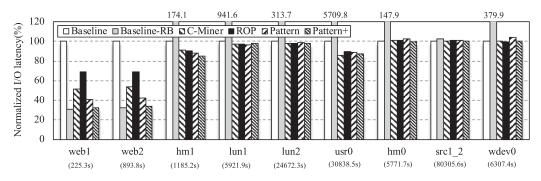

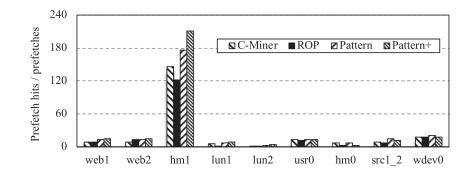

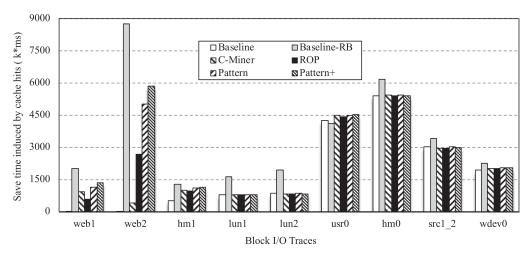

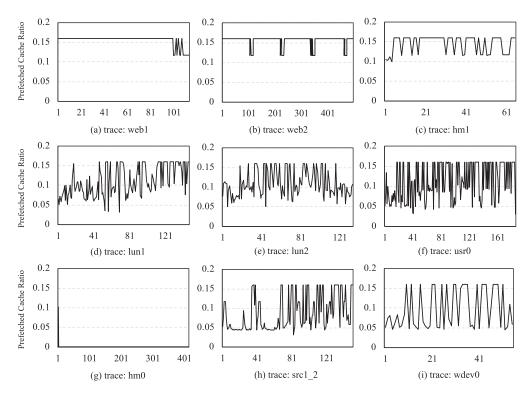

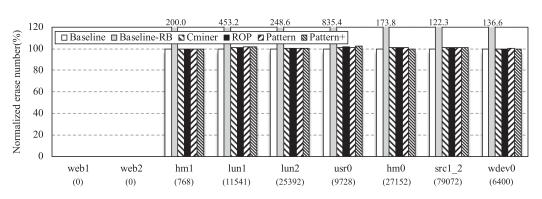

| $14 \qquad lru_replace(req \rightarrow size, rep_flag)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |